#### **Introduction to Logic Gates**

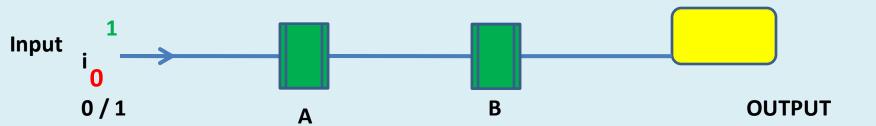

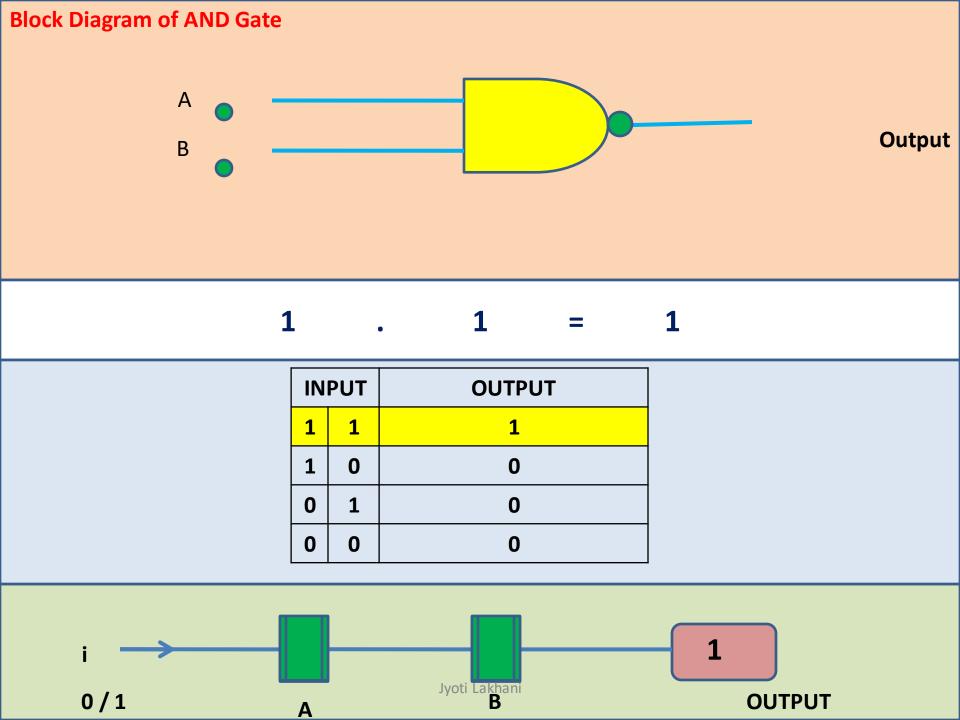

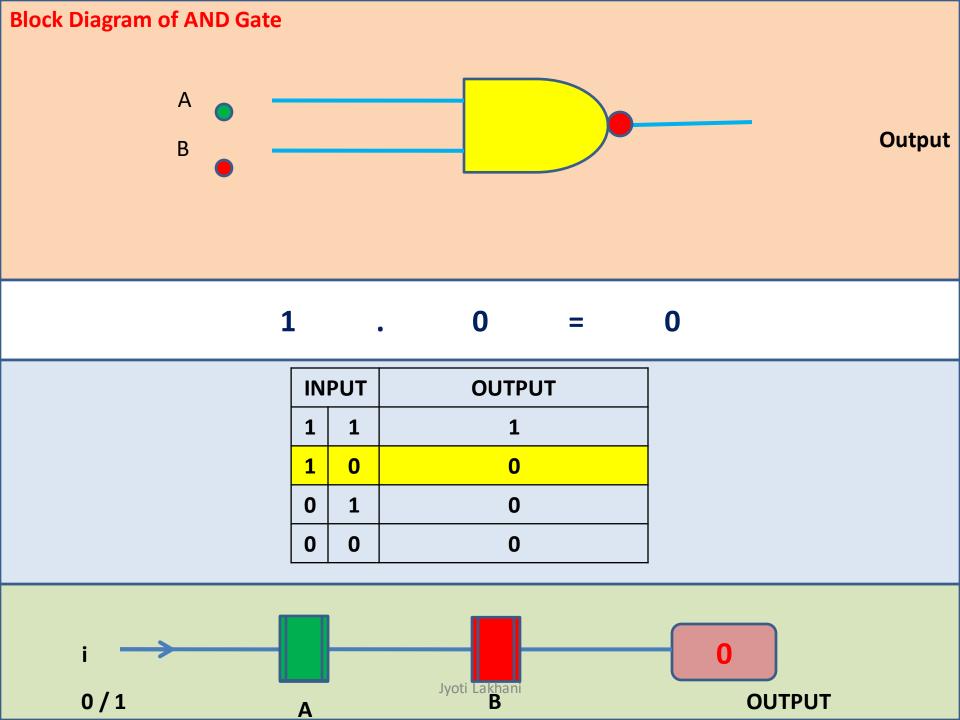

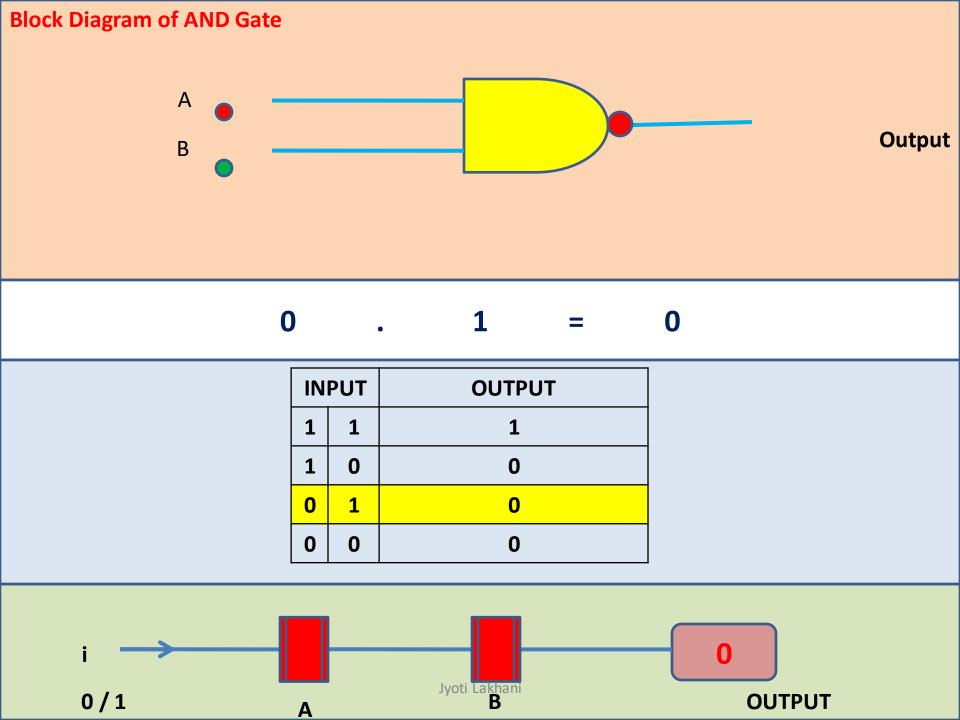

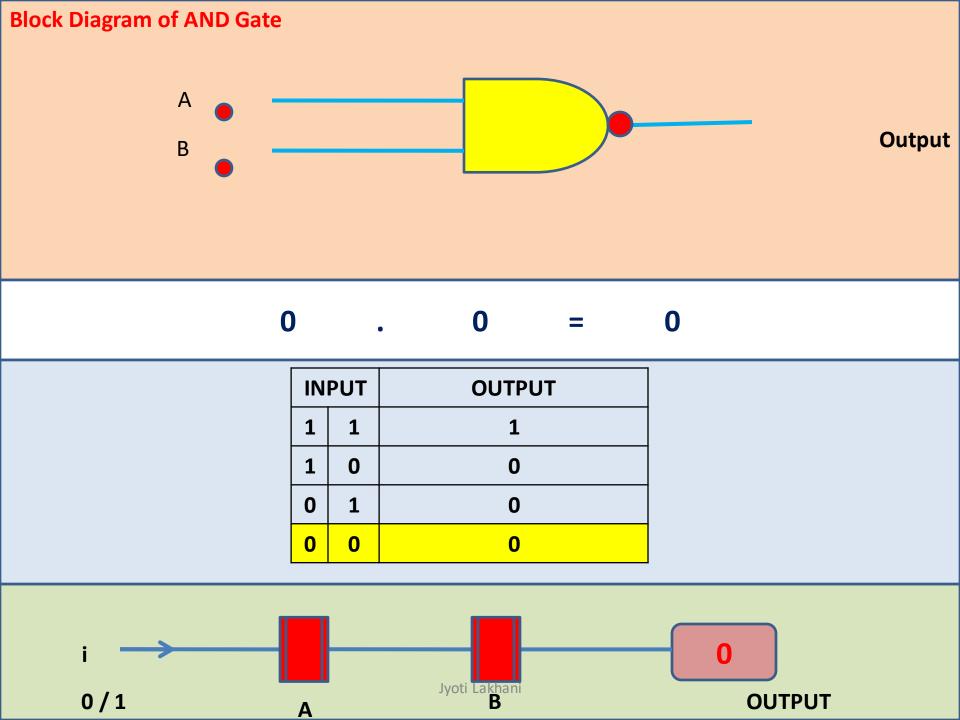

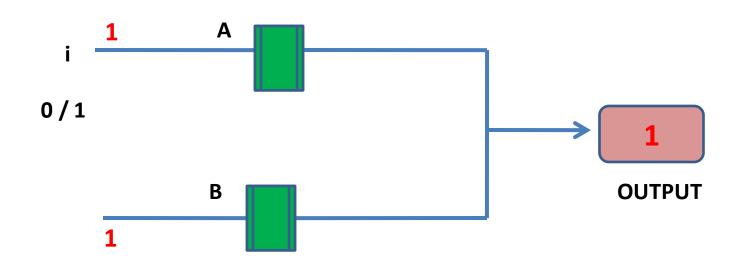

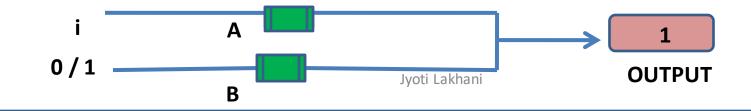

#### **AND Gate**

It is an electronic circuit, which generates an output signal of 1 if and only if all input signals are also 1

An AND gate is the physical realization of the logical multiplication (AND operation)

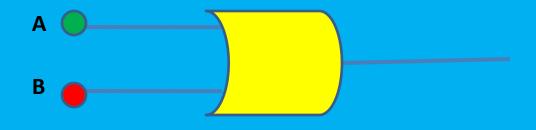

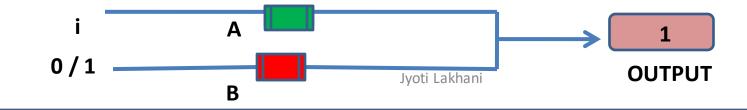

# Suppose Inputis 10

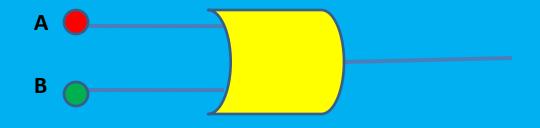

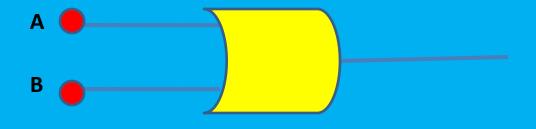

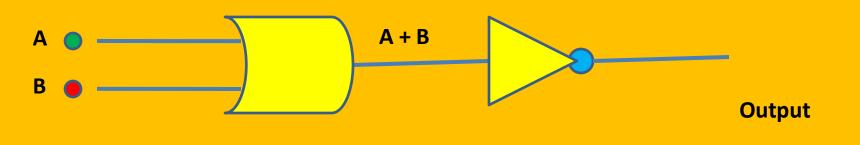

It is an electronic circuit,

which generates an output signal of 1, if any of the output signals is 1

It is the physical realization of logical OR

| INPUT |   | OUTPUT |

|-------|---|--------|

| 1     | 1 | 1      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 0     | 0 | 0      |

| INPUT |   | OUTPUT |

|-------|---|--------|

| 1     | 1 | 1      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 0     | 0 | 0      |

$$0 + 1 = 1$$

| INPUT |   | OUTPUT |

|-------|---|--------|

| 1     | 1 | 1      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 0     | 0 | 0      |

| $\mathbf{\cap}$ | + | lacksquare | _ | $\cap$ |

|-----------------|---|------------|---|--------|

| U               |   | U          | _ | U      |

| IN | PUT | OUTPUT |

|----|-----|--------|

| 1  | 1   | 1      |

| 1  | 0   | 1      |

| 0  | 1   | 1      |

| 0  | 0   | 0      |

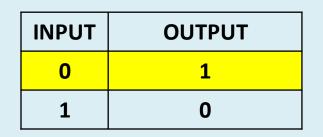

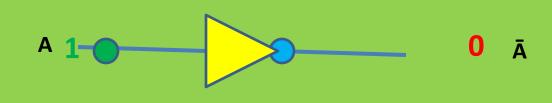

#### **NOT Gate**

It is an electronic circuitthat generates an output signal, which is reverse of input signal It is the physical realization of complementation operation

Not Gate is also called inverter because it inverts the input.

### **NOT Gate**

| INPUT | ОИТРИТ |

|-------|--------|

| 0     | 1      |

| 1     | 0      |

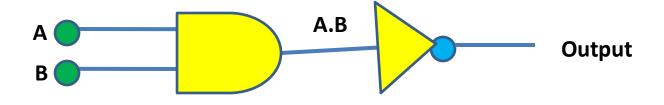

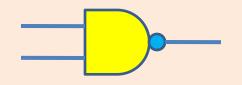

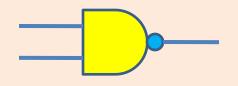

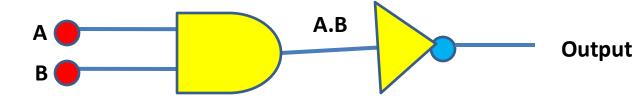

Not AND Gate - NOT + AND gate

It is a combination of NOT and AND gates

It is Complemented AND Gate

#### **Equation of NAND Gate**

$$A \uparrow B = \overline{A \cdot B} = \overline{A} + \overline{B}$$

| INI | PUT | OUTPUT |

|-----|-----|--------|

| 1   | 1   | 0      |

| 1   | 0   | 1      |

| 0   | 1   | 1      |

|     |     | 1      |

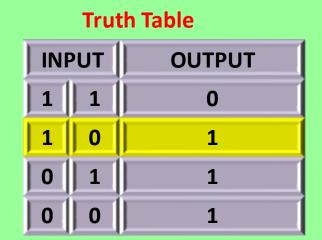

**Truth Table**

Not AND Gate - NOT + AND gate

It is a combination of NOT and AND gates

It is Complemented AND Gate

#### **Equation of NAND Gate**

$$A \uparrow B = \overline{A \cdot B} = \overline{A} + \overline{B}$$

| 1    | ı |   | ١. | l_ |   |   |

|------|---|---|----|----|---|---|

| Jyot | L | a | K  | n  | a | n |

Not AND Gate - NOT + AND gate

It is a combination of NOT and AND gates

It is Complemented AND Gate

#### **Equation of NAND Gate**

$$A \uparrow B = \overline{A \cdot B} = \overline{A} + \overline{B}$$

## Truth Table

| INF | TU | OUTPUT |

|-----|----|--------|

| 1   | 1  | 0      |

| 1   | 0  | 1      |

| 0   | 1  | 1      |

| 0   | 0  | 1      |

It is Complemented AND Gate

Not AND Gate - NOT + AND gate

It is a combination of NOT and AND gates

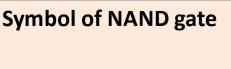

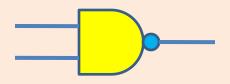

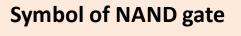

Symbol of NAND gate

#### **Equation of NAND Gate**

$$A \uparrow B = \overline{A \cdot B} = \overline{A} + \overline{B}$$

Jyoti Lakhani

###

**Truth Table**

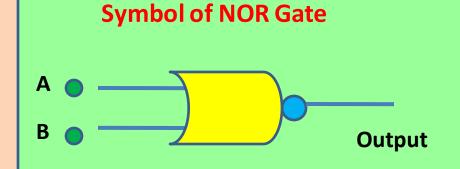

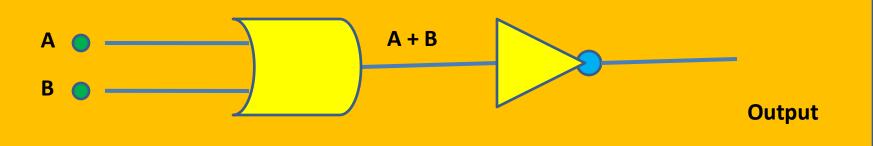

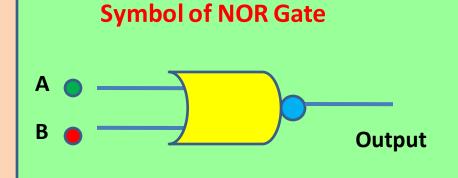

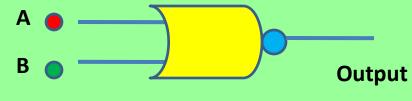

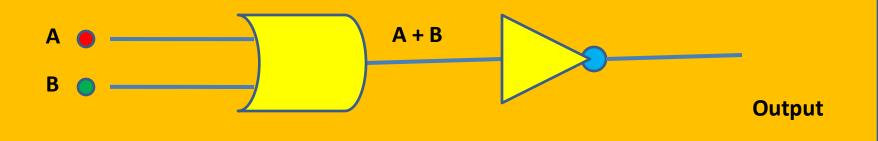

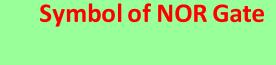

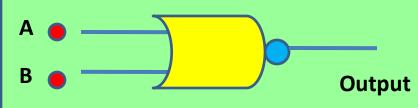

NOT – OR Gate

**NOT Gate + OR Gate**

It is complement OR gate

$$1 + 1 = 0$$

#### **Equation of NOR Gate**

$$A \uparrow B = \overline{A + B} = \overline{A} \cdot \overline{B}$$

#### **Truth Table**

| INF | PUT | ОИТРИТ |

|-----|-----|--------|

| 1   | 1   | 0      |

| 1   | 0   | 0      |

| 0   | 1   | 0      |

| 0   | 0   | 1      |

NOT – OR Gate

**NOT Gate + OR Gate**

It is complement OR gate

$$1 + 0 = 0$$

#### **Equation of NOR Gate**

$$A \uparrow B = \overline{A + B} = \overline{A} \cdot \overline{B}$$

#### **Truth Table**

| INF | TU | OUTPUT |

|-----|----|--------|

| 1   | 1  | 0      |

| 1   | 0  | 0      |

| 0   | 1  | 0      |

| 0   | 0  | 1      |

NOT – OR Gate

**NOT Gate + OR Gate**

It is complement OR gate

$$0 + 1 = 0$$

#### **Equation of NOR Gate**

$$A \uparrow B = \overline{A + B} = \overline{A} \cdot \overline{B}$$

#### **Truth Table**

| INPUT | ОИТРИТ |

|-------|--------|

| 1   1 | 0      |

| 1 0   | 0      |

| 0 1   | 0      |

| 0 0   | 1      |

NOT – OR Gate

NOT Gate + OR Gate

It is complement OR gate

$$0 + 0 = 1$$

#### **Equation of NOR Gate**

$$A \uparrow B = \overline{A + B} = \overline{A} \cdot \overline{B}$$

#### **Truth Table**

| INPUT |   | ОИТРИТ |

|-------|---|--------|

| 1     | 1 | 0      |

| 1     | 0 | 0      |

| 0     | 1 | 0      |

| 0     | 0 | 1      |